Ingatan: Evaluasi Sirkuit PCB

July 13, 2021 Leave a comment

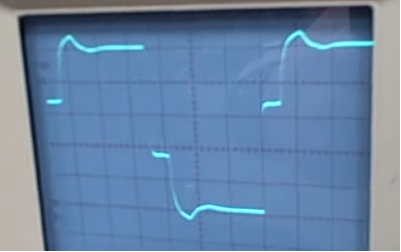

Dahulu, sekitar beberapa tahun yang lalu, saya pernah mengevaluasi board PCB baru untuk dicek kualitas sinyalnya. Setelah itu melakukan rework atau perbaikan kualitas sinyal yang jelek. Caranya yaitu dengan menambahkan/mengganti komponen resistor atau capasitor pada jalur yang telah ada. Yang saya pahami saat itu adalah jika sinyal berosilasi, ya, tambahkan low pass filter komponen RC (resistor capasitor). Pengetahuan saya hanya sebatas low pass filter, dan itu pun hanya metode kira-kira saja, trial and error. Saya sempat menemui beberapa bentuk sinyal diantaranya sinyal overshoot, undershoot, step noise, sirip hiu, dan beberapa bentuk sinyal akibat crosstalk. Terlebih jika mengevaluasi board baru dengan kabel FFC yang panjang yang biasanya bermasalah dengan kualitas sinyal. Ada yang mudah untuk dicounter-measure, ada juga yang sulit sekali. Lalu, mucul banyak pertanyaan dalam benak saya, bagaimana cara meng-counter sinyal-sinyal tersebut? Apakah bisa dihitung? Apakah bisa disimulasikan? Karena jika semua bisa dikalkulasikan/diperkirakan dengan baik maka hal ini akan dengan cepat diselesaikan. Karena waktu itu sibuk dengan pekerjaan, jadi tidak sempat mencari tahu penyebabnya dan membuat simulasinya.

Hampir satu tahun berlalu setelah resign dari perusahaan tersebut, tanpa sengaja saya melihat salah satu video dari Robert Feranec tentang perancangan PCB, terlebih untuk high speed data, bahwa dalam high speed data, urusan impedance harus diperhatikan. Sepertinya pertanyaan-pertanyan saya dahulu mulai mendapat sedikit pencerahan. Sinyal yang saya evaluasi memang mempunyai nilai rise time sekitaran 50ns kalau tidak salah. Kesimpulan dari video itu, intinya impedance dari mulai signal driver sebagai pengirim sinyal, trace (jalur) PCB sebagai transmission line, dan load impedance di bagian penerima sinyal harus mempunyai impendance yang sama untuk mendapatkan transfer daya maksimum serta mengurangi reflection yang bisa mengakibatkan ringing (sinyal berosilasi).

Sumber sinyal dan load bisa berupa IC. Sedangkan untuk transmision line-nya adalah jalur pada PCB, konektor, atau pun kabel. Saya jadi teringat dengan mata kuliah elektro magnetik waktu kuliah dulu. Sayang sekali saya kurang menyimak mata pelajaran tersebut padahal ternyata berguna dalam memahami design PCB. Hehe.

OK, lanjut. Jadi nilai impedance dari transmision line harus disesuaikan agar characteristic impedance Z0 nya mempunyai nilai yang sama dengan ZS dan ZL. Sebagai contoh, untuk koneksi USB biasanya mengharuskan impedance sebesar 90 Ohm. Untuk sinyal LVDS sekitar 100 Ohm. Sedangkan standard untuk nilai impedance adalah 50 Ohm. Tapi, saya tidak menemukan bagaimana menentukan impedance untuk sebuah pin IO dari microcontroller. Saya hanya menemukan jawaban di forum ini link , link dan link tapi informasinya kurang memuaskan.

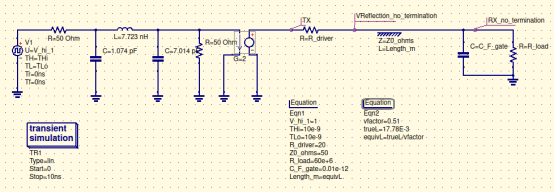

Berikut bentuk model elektronik dari sebuah trace pada PCB.

Pada sebuah PCB, Z0 ini dipengaruhi oleh konstanta dielektrikdari bahan pembuat PCB tersebut, misal FR-4STD mempunyai konstata dielektrik 4.6.

Selanjutnya dipengaruhi oleh lebar jalur, ketebalan tembaga, dan jarak antara jalur dengan reference plane (ground plane) Link. Perhitungan dalam mendisain PCB bisa pakai aplikasi Saturn PCB Toolkit, mulai dari menghitung impedance, crosstalk, dll.

Selain itu, hasil dari pencarian saya di internet tentang control impedance PCB yaitu websitenya JLCPCB yang menyediakan calculator untuk menghitung lebar jalur yang direkomendasikan berdasarkan impedance yang diinginkan.

Setelah menonton beberaapa video dan membaca referensi, ternyata mendisain PCB yang baik itu sulit dan harus mendetail. Berikut beberapa hal penyebab penurunan kualitas sinyal:

- Impedance mismatch

- Frequency respon

- Crosstalk

- Noise

- Jitter

OK, karena penasaran, saya coba mensimulasikan beberapa bentuk sinyal berdasarkan rasa penasaran saya waktu kerja dahulu. Saya sebenarnya ingin mencoba memakai software HyperLynx Signal Integrity. Akan tetapi, ternyata software tersebut berbayar. Maka dari itu, kali ini saya menggunakan software gratis bernama Qucs (Linux, Mac OS, dan Windows).

1.Kasus 1: Ringing

Kasus sinyal ringing pernah saya temui dan lumayan sering. Berdasarkan pengetahuan saya kala itu, saya menambahkan rangkaian RC sebagai low pass filter. Akan tetapi, setelah membaca beberapa atikel, saya mendapat pemahaman baru. Sinyal ringing sendiri bisa bersumber dari power supply, tetapi bisa juga akibat dari jalur/trace yang panjang. Jika kita sudah mempunyai jalur yang pendek dan masih terjadi ringing, maka bisa jadi disebabkan oleh parasitic inductance dan capacitance dari komponen. Jika mempunyai jalur yang panjang, ringing disebabkan reflection dari sinyal dikarenakan impedance mismatch.

Sekarang saya akan coba simulasikan pengaruh panjang trace terhadap ringing dengan patokan critical length. Jika panjang jalur sama atau melebihi critical length, maka harus dilakukan kontrol impedance pada transmission line tersebut yaitu harus match impedance. Critical length dirumuskan dengan L < 2 xRT, dimana L dalam inch dan RT (rise time) dalam ns.

Untuk meng-generate sinyal kotak yang smooth saya menggunakan bessel lowpass filter untuk memfilter sinyal kotak rise time 0ns dengan frekuensi cut-off 1GHz. Nilai rise timenya Tr = 0.35/f3dB dengan perhitungan bahwa nilai rise time dihitung pada sasat perpindahan sinyal kotak 10% menuju 90% dari voltage sinyal HIGH. Karena jika menggunakan nilai rise time dari Qucs, betuk sinyalnya kaku.

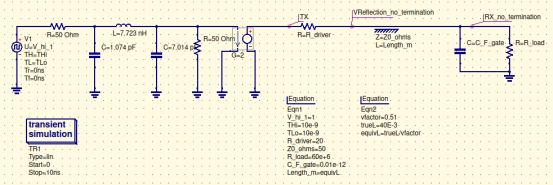

Model Ideal transmission line di Qucs mempunyai propagation velocity 3×108 m/s atau sekitar 11.8 inch/ns, yang merupakan kecepatan transmisi di udara. Sedangkan untuk sebuah PCB dengan bahan FR4 memiliki kecepatan sekitar 6 inch/ns. Maka kita akan masukan rumus velocity factor 6/11.8 = 0.51 ke perhitungan transmission line. Nilai R_driver dibuat 20 Ohm agar Zsource missmatch impedance dengan Z0 (characteristic impedance) transmission line. Untuk nilai variable di load, kurang lebih saya mengikuti nilai di dokumen berikut: Rload = 60M Ohm sedangkan untuk input capacitancenya saya buat kecil saja sehingga bisa diabaikan karena efek input capacitance ini akan mempengaruhi respon sinyal terhadap waktu.

Nilai rise time dari sinyalnya sekitar 0.35 ns. Maka, berdasarkan rumus di atas, max length nya adalah 2 x 0.35 = 0.7 inch = 17.78 mm. Saya coba dengan panjang 15 mm dan tidak terjadi ringing. Berarti pada jalur trace yang pendek matching impedance bisa diabaikan.

Kemudian saya ubah menjadi 17.78 mm dan mulai terjadi ringing. Berarti sesuai rumus L < 2 xRT, jika L panjang maka trace perlu matching impedance.

Semakin bertambah panjang transmission line, maka semakin besar amplitudo ringingnya. Saya coba dengan panjang 40 mm.

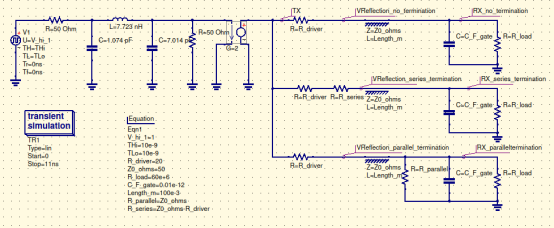

Lalu bagaimana jika jalur kita mengharuskan panjangnya melebihi panjang maksimum dari rumus di atas? Maka kita harus memperhatikan impedance dari transmission line agar match. Berikut sinyal ringing yang saya simulasikan dengan panjang trace 100 mm atau 10cm, serta pemasangan termination resistor sebagai solusinya di aplikasi Qucs agar matching impedance. Kali ini saya abaikan velocity factor dari FR-4, jadi tidak saya masukan ke rumus. Dan juga saya hanya mensimulasikan termination resistor series dan parallel saja.

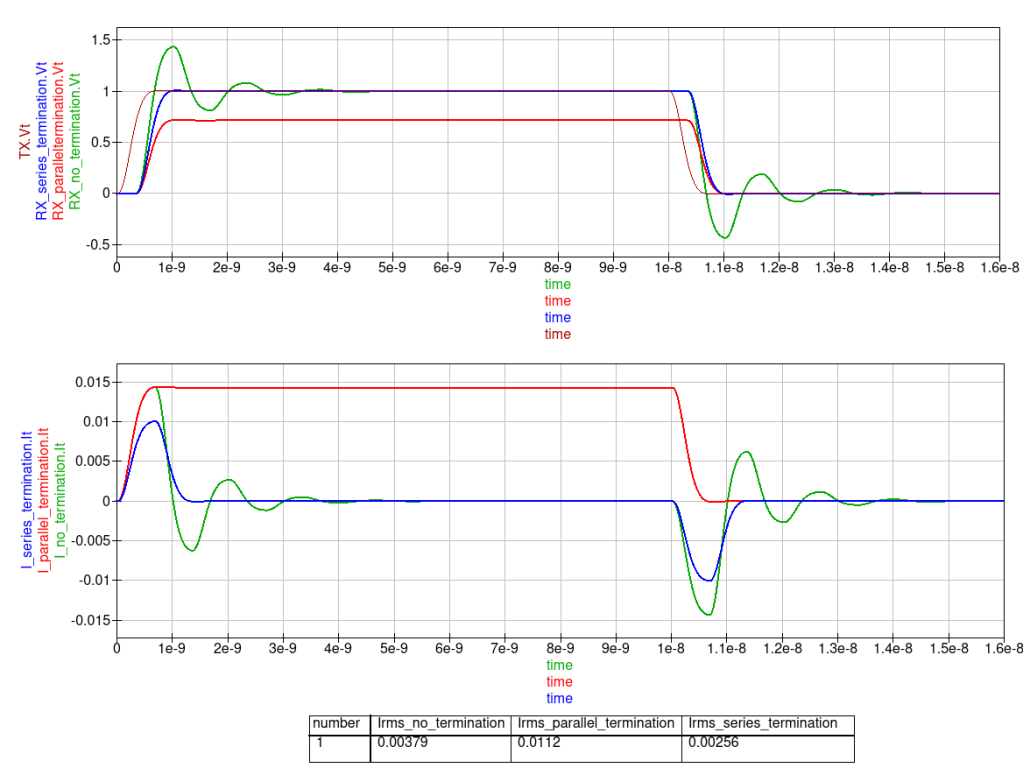

Berikut adalah simulasi untuk melihat efek dari missmatch impedance dan setelah pemasangan termination resistor series dan parallel.

Source Termination: Add series resistor at driver. Value RT = Z0 – RS. If RS is small, then RT = Z0.

Load Termination: Add parallel resistor at receiver. Value such that RL // RT = Z0. If RL is large, then RT = Z0.

Penambahan termination resistor menghasilkan sinyak yang OK.

Ada beberapa metode dalam menambahkan termination resistor, cek link berikut.

Kelebihan series termination:

- Simpel, hanya memerlukan satu resistor

- Konsumsi daya rendah

- Sebagai pembatas arus ketika mendrive beban capasitif yang besar, hal ini juga menigkatkan performa jitter dengan mengurangi ground bouce.

Sedangkan kelemahannya adalah:

- Meningkatkan rise time dan fall time sinyal di sisi load. Hal ini terkadang tidak bisa ditoleransi dalam beberapa aplikasi high speed.

- Tidak dapat mendrive banyak load.

Sedangkan untuk parallel termination:

- Bisa menghasilkan sinyal yang lebih jernih dan mengeliminasi reflection pada sisi beban. Termination ini harus dipasang sedekat mungkin dengan beban.

- Konsumsi arus yang besar. Tidak direkomendasika untuk aplikasi low power.

- Falling edge akan lebih cepat dari pada rising edge, maka memungkinkan perubahan duty cycle pada sinyal clock.

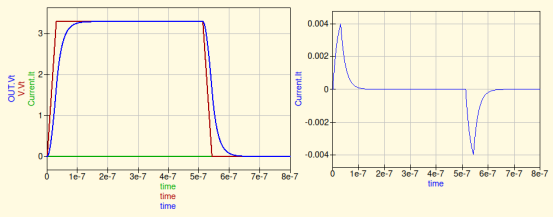

Berikut adalah kurva arus dari masing-masing termination. Parallel termination mempunyai Irms yang besar yaitu 0.0112 A. Sedangkan series termination mempunyai Irms yang kecil yaitu 0.00256 A.

Selain itu, series termination hanya dapat mengeliminasi reflection pada sisi end load saja. Dan hal ini tidak baik untuk topology banyak receiver.

Sedangkan parallel termination bisa mengeliminasi reflection di semua point karena itu cara ini cocok untuk topology banyak receiver seperti bus clock. Tetapi sinyal yang dihasilkan menjadi terpotong karena efek pembagi tegangan dari RS dan RT.

Kita lihat hasil simulasi berikut yang menunjukan reflection sinyal yang di ukur di node VReflection.

Berikut contoh reflection signal pada sebuah kabel tanpa termination.

Lalu bagaimana jika saya tambahkan komponen input capacitance yang tadinya kita coba abaikan dengan mensetting kecil sekali, sekarang kita ubah menjadi 15pF.

Simulasi L < 2xRT

Dengan penambahan variable input capacitance 15pF, sinyal yang tadinya pada nilai L = 15 mm tidak ada osilasi, sekarang menjadi ada osilasi. Padahal nilai critical lenghtnya 17.78 mm. Selain itu, signal propagation delaynya bertambah lebar.

Simulasi pada L = 40 mm.

Simulasi L > 2xRT, resistor termination

Penambahan variable input capacitance 15pF menjadikan bentuk sinyal lebih kompleks.

Permasalahan impedance memang menjadi hal penting dalam signal integrity. Untuk mengukur impedance, salah satu metodologi yang digunakan adalah TDR (Time Domain Reflectometry). TDR mengukur reflection dari sinyal pulse yang ditransmisikan melalui sebuah transmission line (jalur PCB, kabel, konektor, dll) yang akan diamati.

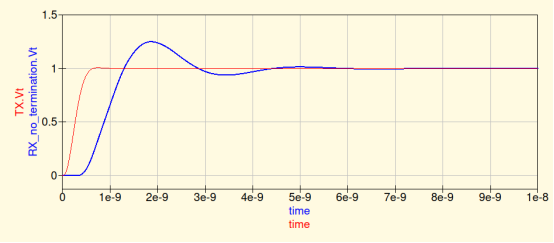

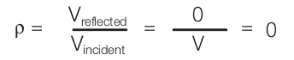

Pengukuran TDR dideskripsikan dengan Reflection Coefficient ρ (rho). ketika ZL sama dengan Z0 maka match impedance dan tidak ada reflection.

Ketika ZL terbaca nol yang menandakan short circuit. Sinyal reflected wave sama dengan incident wave tapi mempunyai polaritas yang berlawanan. Rho bernilai -1.

Ketika ZL bernilai tak hingga atau open circuit, reflected wave sama dengan incident wave dan mempunyai polaritas yang sama. Rho bernilai 1.

Nilai dari ZL dan Z0 dapat dihitung dengan persamaan berikut.

Pada zaman sekarang banyak perangkat osiloskop yang sudah bisa mengukur TDR. Pengukuran TDR biasa ditampilkan dengan satuan volt, ohm atau rho pada sisi vertical dan time/waktu pada sisi horizontal. Berikut beberapa efek sinyal yang dihasilkan terhadap beberapa bentuk transmission line dan load.

Rise time, settling time, dan pulse aberraton dapat mempengaruhi pengukuran TDR.

Saya coba mensimulasikan pengukuran TDR ini di software Qucs. Saya menggunakan sebuah pulse dengan rise time yang cepat dengan nilai 10 ps dan saya tambah delay agar sinyal tidak rapat di time nol, maka saya kasih delay 500ps.

Dari kurva rho bisa kita ukur panjang dari line yang match impedance yaitu dari 5.22e-10 s sampai 2.5e-09 s. Dengan asumsi kecepatan sinyal pada ideal transmission line di Qucs sama dengan velocity di udara, 11.8 inch/ns, dan panjang Tp transmission line sama dengan 2Tp panjang di kurva rho, maka bisa dihitung panjang transmission line. Len = ((2.5E-9ns – 0.522E-9ns)*11.8inch/ns)/2 menghasilkan nilai 11.67 inch atau sekitar 296.42 mm mendekati ~300mm. Pada kurva Z_firstorder juga bisa dilihat impedance di load sekitar 1e4 atau 10K Ohm.

Saya coba denga nilai yang bervariasi.

Pada rho bernilai 1 menandakan load bernilai besar seperti open circuit terletak pada time 1.92e-9 s. Sekilas bisa kita lihat nilai impedance yang terukur sekitar 100, 50 dan 120 Ohm dengan perbandingan panjang menyerupai 0.1, 0.04, 0.07 m. Ini hanya sebatas simulasi. Mungkin pada pengukuran aslinya, masalahnya akan lebih kompleks.

2.Kasus 2: Clock Distribution.

Dahulu saya menemukan sinyal seperti sirip hiu ketika harus mengevaluasi sebuah sinyal yang terkoneksi antara main board dan sebuah panel board baru dengan koneksi kabel FFC yang lumayan panjang. Ya, seingat saya sepert itu. Kalau tidak salah di jalur bus clock yang didistribusikan ke 3 IC shift register untuk LCD driver dan keypad. Sinyal tersebut masuk kategori NG karena nilai rise timenya terlalu besar sehingga tidak masuk standard. Oleh karena itu, dengan pengetahuan yang terbatas, alias ilmu kira-kira, saya mencoba memodif rangkaian circuit nya dengan trial and error nilai komponrn RC di jalur tersebut. Susah sekali mendapatkan sinyal yang OK. Akhirnya saya mencukupkan usaha saya, yang penting tetap memenuhi standar electrical characteristic di datasheet. Beginilah kira-kira bentuk sinyalnya. Saya coba mensimulasikannya di Qucs dengan nilai perkiraan bahwa output impedance sebuah IC driver adalah ideal 50 Ohm dan input impedance receiver adalah 1M merujuk pada dokumen ini link. Sedangkan transmission line impedancenya kita setting 10 Ohm. Berikut hasilnya.

Ternyata sinyal sirip hiu tersebut muncul ketika terjadi penurunan impedance antara 50 Ohm di Rs menuju 10 Ohm di transmission line. Standarnya, jalur PCB itu harus punya impedance 50 Ohm. Tetapi saya masih belum yakin hal ini dikarenakan impedance di trace PCB. Saya sempat ukur sinyal di PCBnya saja tanpa dihubungkan ke panel board, hasilnya OK. Berati PCB trace di main board tidak bermasalah. Lalu, saya menemukan sebuah artikel yang menyebutkan bahwa ketika mendistribusikan sinyal clock, maka akan beresiko mengurangi kualitas sinyal.

Dalam artikel tersebut disebutkan bahwa jika satu sumber clock digunakan untuk men-drive banyak beban, maka akan terjadi penurunan kualitas sinyal jika total load/beban melebihi kapasitas sumber clock. Gejala yang muncul biasanya adalah clipping, symmetry imbalance, penurunan amplitude sinyal dan perubahan rise dan fall time, dan hal ini seiring juga dengan peningkatan frekuensi sumber clock.

Saya teringat, memang design clock source ini dibagi ke 3 IC shift register di panel board dan mempunyai frekuensi yang besar. Lalu, berdasarkan artikel ini bahwa IC CMOS mempunyai input capacitance sekitar 15pF dan input resistance sekitar 60M Ohm. Ya, memang setiap device mempunyai nilai paracitic capacitance.

Mungkin inilah penyebabnya (input capacitance) yang menyebabkan nilai rise time menjadi besar. Jika jalur clock di distribusikan ke banyak komponen, maka beresiko memperlebar rise time. Saya juga menemukan dokumen ini yang menyebutkan bahwa drive strength dari sebuah pin output juga mempengaruhi nilai rise time. Drive strength adalah salah satu fitur dari pin mikrokontroller yang bisa mengatur kemampuan pin untuk bisa memilih arus maksimum yang bisa dikeluarkan untuk mendrive load. Diatur melalui register dengan pilihan biasanya 2, 4, 6,dan 8mA.

Lalu saya coba mensimulasikannya di Qucs dan transmission linenya saya tidak pakai karena saya anggap masalahnya bukan di jalur PCBnya. Untuk mensimulasikan drive strength saya menggunakan resistor limiter untuk membatasi arus dari voltage source. Nilainya adalah 1650, 825, 550, 412.5 untuk merepresntasikan drive strength 2, 4, 6, dan 8 mA dengan menggunakan rumus V=IxR. Untuk setingan clock source, saya menggunakan sebuah datasheet dari color LCD 1.4 inch untuk mensimulasikan kebutuhan clock paling kritis dari board panel. Nilai rise time saya pakai 30ns dan frekuensi 1.84MHz atau perioda 543ns. Pertama, saya coba mendrive satu load dengan drive strength 2mA atau dengan resistor limiter 1650 Ohm. Ketika source clock mendrive satu load, sinyalnya masih OK.

Akan tetapi, ketika mendrive 3 load, nilai rise time bertambah.

Terkadang, rise time yang cepat juga akan mengakibatkan forward crosstalk. Semakin cepat rise time makan semakin besar pula amplitude crosstalk dan semakin tajam pula sinyal crosstalknya. Akan tetapi, jika memang rise time nya terlalu besar dan menjadi di luar batas spesifikasi, maka harus diperbaiki. Berdasarkan dokumen sebelumnya bahwa dengan meningkatkan drive strength maka nilai rise time akan semain cepat. Sekarang kita akan coba untuk mengganti drive strength menjadi 8 mA atau dengan mengganti resistor limiter menjadi sekitar 412 Ohm.

Ya, hasilnya rise time menjadi lebih cepat. Jika dilihat dari spike konsumsi arus, untuk drive strength 2mA (1650 Ohm) 1 load adalah 1.16mA, dan drive strength 2mA (1650 Ohm) 3 load adalah 1.64mA, terlihat konsumsi arus tidak sampai 3 kali dari load. Tetapi jika driver strength 8mA (412 Ohm) 3 load adalah sekitar 4mA, konsumsi arus sekitar 3 kali bahkan lebih dari yang 2mA 1 load.

Jika kita memperhatikan impedance, berikut beberapa tipe routing untuk multiload clock.

Daisy Chain Routing/Fly-by Topology/ Multi-drop Topology

–With Stubs

Semakin pendek stub, maka semakin sedikit reflection. Karena stub yang panjang bisa mengakibatkan perbedaan impedance dan akan berpengaruh terhadap sinyal. Berikut perbedaan sinyal akibat panjang stub.

-Witout Stubs

Kelemahan dari tipe routing seperti ini adalah ada perbedaan time propagation delay dari setiap device. Device yang lebih dekat mempunyai time propagation delay yang sedikit. Tentu saja untuk device yang memerlukan akurasi waktu, tipe ini tidak cocok. Memory DDR3 dan DDR4 memugkinkan untuk memakai memakai topology ini. Sedangkan memory DDR2 biasanya memakai T-topology. T-topology akan mengakibatkan akumulasi perbedaan impedance di cabangnya. Sehingga akan bermasalah pada frequensi yang tinggi. Karena itu, DDR3 dan DDR4 biasanya memakai fly-by topology.

Star Routing

Pada topology ini, sinyal berjalan dengan waktu yang sama. Jalur harus sama untuk menghindari waktu sinyal yang tidak simetris terhadap time delay.

T-topology